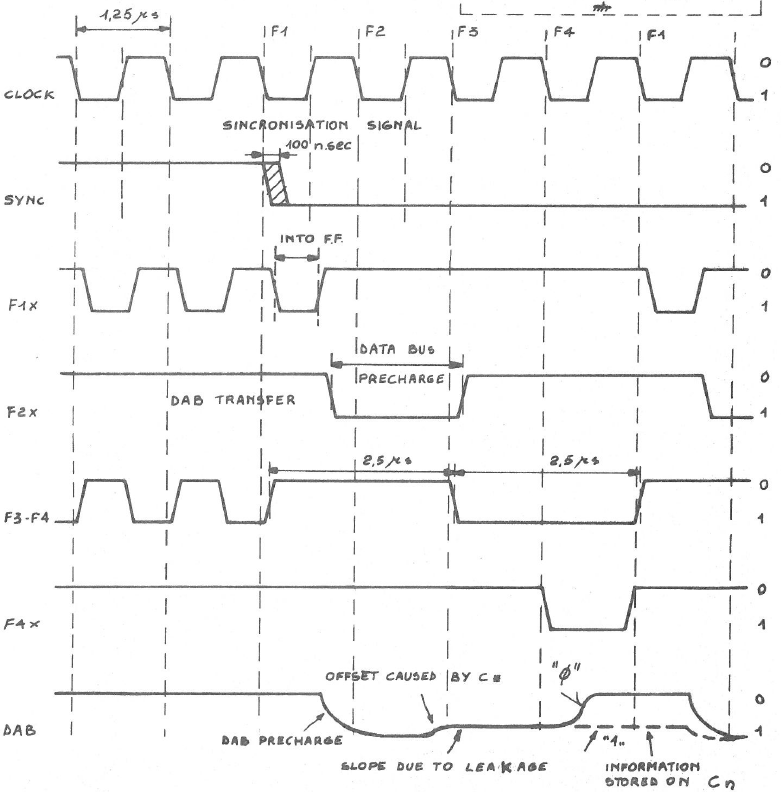

Base-timing:

Der CP3F braucht 4 Takte für einen Befehlszyklus:

Die vier Taktphasen:

F1:

F2: Precharge

F3:

F4:

Precharge Datenbus:

Der Datenbus der CP3F CPU hat eine Besonderheit: Jede Leitung des Datenbusses (DAB) braucht eine externe Kapazität (CL 200..300pf). Nur die CPU lädt dann jede Buskapazität im der Phase2 auf 0V (also logisch 0); alle anderen Busteilnehmer ziehen dann die entsprechende Datenleitung nur auf 5V (log. 1) in der 4 Phase. Die 0 bleibt dann auf dem Kondensator einfach erhalten.

So sieht die Schaltung in den original Unterlagen aus:

Auf meinem Board sieht die externe Beschaltung des CP3F dann so aus (C1 bis C8):

fallen, dies könnte sonst die Chips beschädigen.

-------------------------------------------------------------------------------------------------------------

<-prev >Top< >Hardware< Last Modified: 6.April.2025 Impressum ->next: