Versorgung:

Der CP3F und auch die RAM/ROM und IO-Bausteine (M830, M381, M382 und M383) brauchen drei Versorgungsspannungen 0V, -5V und -12V .

In der Dokumentation (SGS_38_cp3f_cpu) werden die 3 Spannungen so bezeichnet:

Bezeichnung | Spannung | Alternativ |

VSS | 0V | +5V |

VDD | -5V | GND |

VGG | -17V | -12V |

Etwas verwirrend ist das die Doku die Spannungen manchmal alternativ +5V, GND und -12V

verwendet. Ich verwende in meiner Doku die Alternativbezeichnungen.

Jeder der Chips braucht so typisch ca. 500mW.

Takt und Reset(Sync):

Die CPU und deren original IO-Bausteine brauchen den Takt und den Reset (als SYNC

bezeichnet) mit +5V und -12V Pegeln, die Waveform dazu (aus SGS_38_cp3f_cpu Seite 8):

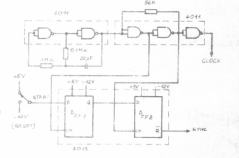

Der Schaltungsvorschlag aus der Dokumentation:

Da bei meinem Aufbau der Takt- und das Resetsignal im FPGA (mit +5V / 0V Pegel)

erzeugt werden, kommt dieser Levelshifter anstelle obiger Schaltung zur Verwendung:

(Die Vorwiderstände und die Dioden sollen die Gates der PMOS-Transistoren vor ESD schützen.)

Das sieht am Oszi dann so aus:

Oben: Eingang CLK5V - das 5Volt CMOS Signal.

Unten: CLK17V der Takt für den CP3F mit +5Volt und -12 Volt Pegel.

-------------------------------------------------------------------------------------------------------------

>Top< >Hardware< Last Modified: 5.Apr .2025 Impressum ->next: